Hardware Description Language | VLSI Tutorial | Mepits

Hardware Description Language

Hardware description language (HDL) is a specialized computer language used to program electronic and digital logic circuits. The structure, operation and design of the circuits are programmable using HDL. HDL includes a textual description consisting of operators, expressions, statements, inputs and outputs. Instead of generating a computer executable file, the HDL compilers provide a gate map. The gate map obtained is then downloaded to the programming device to check the operations of the desired circuit. The language helps to describe any digital circuit in the form of structural, behavioral and gate level and it is found to be an excellent programming language for FPGAs and CPLDs.

The three common HDLs are Verilog, VHDL, and SystemC. Of these, SystemC is the newest. The HDLs will allow fast design and better verification. In most of the industries, Verilog and VHDL are common. Verilog, one of the main Hardware Description Language standardized as IEEE 1364 is used for designing all types of circuits. It consists of modules and the language allows Behavioral, Dataflow and Structural Description. VHDL (Very High Speed Integrated Circuit Hardware Description Language) is standardized by IEEE1164. The design is composed of entities consisting of multiple architectures. SystemC is a language that consist a set of C++classes and macros. It allows electronic system level and transaction modeling.

Need for HDLs

The Moore’s Law in the year 1970 has brought a drastic change in the field of IC technology. This change has made the developers to bring out complex digital and electronic circuits. But the problem was the absence of a better programming language allowing hardware and software codesign. Complex digital circuit designs require more time for development, synthesis, simulation and debugging. The arrival of HDLs has helped to solve this problem by allowing each module to be worked by a separate team.

All the goals like power, throughput, latency (delay), test coverage, functionality and area consumption required for a design can be known by using HDL. As a result, the designer can make the necessary engineering tradeoffs and can develop the design in a better and efficient way. Simple syntax, expressions, statements, concurrent and sequential programming is also necessary while describing the electronics circuits. All these features can be obtained by using a hardware description language. Now while comparing HDL and C languages, the major difference is that HDL provides the timing information of a design.

HDL Structure & Design

Generally, HDL structure consist a textual description involving many inputs, outputs, signals operators, components, multiple architectures, and comments. Concurrent and sequential way of programming style is possible in HDL. Each and every HDL uses a different structure and design method. The examples shown below using VHDL and Verilog will help to get an overall idea about HDL structure and design.

VHDL: AND GATE EXAMPLE

- Using Data Flow Modeling: Data Flow Modeling in VHDL shows the flow of the data from input to output. In the AND gate example, first the library definitions are given. Then the entity declaration. Entity or the architectural body of the AND gate includes the inputs ‘a’, ‘b’, output ‘c’ and the entity name ‘AND1’.Here the data type of the input and output is bit type which represents 0 and 1 values. Generally in VHDL data types are classified as scalar, composite, access, standard logic and file types.The words in color are the generally known as reserved words in VHDL. After the entity description, the architecture is defined, which involves the design of the gate. ‘<=’ represents the assignment operator. In this ‘and’ is the logical operator representing the function. The relational, logical, adding, miscellaneous, sign and multiplying are generally the operators present in VHDL.

Figure 1: VHDL Data Flow Model of AND Gate

- Using Structural Modeling: Structural Modeling in VHDL helps to model any circuit by specifying the components used in them. The model will clearly define the interconnections also. Here each component in the circuit is modeled as an entity. In the structural AND gate example, after defining the library and the entity, the component is defined. After the ‘begin’ statement in the architecture, the function of the component in the circuit is defined using the inputs, signals and outputs. This model allows a hierarchical design.

Figure 2: VHDL Structural Model of AND Gate

- Using Behavioral Modelling: It uses constructs similar to C language.In this model, we can use if-else, for loops, while statements and case statements too.

Figure 3: VHDL Behavioral Model of AND Gate

Verilog: OR GATE EXAMPLE

- Using Data Flow Modeling: Instead of using the assignment operator, it uses the continuous assignment statement with the keyword ‘assign’. Verilog generally defines each circuit using a module. The module will generally involve the name of the design, its inputs and outputs and functionality. In the OR Gate example ‘orgate’ is the module name. In Verilog we generally use wires and registers to define the variables.Here the OR function is represented by using the operator ‘|’.Generally, Verilog involves arithmetic, logical, relational, equality, bitwise, reduction, shift, concatenation, replication and conditional operators.

Figure 4: Verilog Data Flow Model of OR gate

- Using Structural Modeling: In this model, the component represents another design module.

Figure 5: Verilog Structural Model of OR Gate

- Using Behavioral Modeling: In Verilog, this model is exactly similar to C.Here we use always block were the statements are written.Reg is used to declare the variable.

Figure 6: Verilog Behavioral Model of OR Gate

HDL Simulation & Debugging

HDL Simulation involves the need of a test bench. A test bench is an environment used to check the correctness of the design. The test bench involves the inputs, outputs and the procedure to be done. The HDL simulator will execute the test bench; thereby the designer can verify the function of the circuit on the waveform analyzer provided by the HDL simulator. Many simulators are there for HDLs.

Debugging can be done before and after simulation. If errors are present, the HDL simulators usually give an error report and thereby corrections can be done. Also, by checking the simulation result the errors can be found and rectified. ModelSim, Xilinx ISim, Aldec Active - HDL are some examples of HDL simulators.

Figure 7: OR Gate Simulation Waveform from Xilinx ISim

Figure 8: AND Gate Simulation Waveform from Xilinx ISim

Different Types of HDLs

Different HDLs are available for describing analog circuits, digital circuits and PCBs.

HDLs for digital circuit design: Other than Verilog, VHDL and SystemC many HDLs are available for digital circuits. Among them, Advanced Boolean Expression Language (ABEL) is better for programming PLDs (Programmable Logic Devices). It includes sequential and concurrent logic formats, truth table formats and describes test vectors also. Altera Hardware Description Language (AHDL), a language from Altera is used for CPLDs and FPGAs. All language constructs can be used in AHDL providing more control and support. Bluespec, a high level functional programming HDL language is developed to handle chip design and automation systems. Bluespec System Verilog (BSV) uses syntax similar to Verilog HDL. C-to-Verilog is generally a converter which helps to convert C to Verilog language. Constructing Hardware in a Scala Embedded Language (Chisel), MyHDL and HHDL are HDLs used to support advanced hardware design.

Confluence and CoWareC are the two languages which were discontinued after the arrival of the System C language. Compiler for Universal Programming Language (CUPL) is generally used for logic device programming. Handel-C is used for programming FPGA’s. Hardware Join Java (HJJ) helps in reconfigurable computing applications. Impulse C, subset of C supports parallel programming. Just-Another Hardware Description Language (JHDL) uses an object oriented programming approach. LavaHDL helps in specifying layout of circuits mainly. Lola HDL is basically used for synchronous digital circuits. M, is another HDL from Mentor Graphics. PALASM is used as a HDL for Programmable Array Logic (PAL) devices. Finally System Verilog is an extension to Verilog.

HDLs for analog circuit design: The HDLs used for analog circuits include Analog Hardware Description Language (AHDL), Spectre High Level Description Language (SpectreHDL), Verilog for Analog and Mixed Signal (Verilog – AMS), VHDL with analog and mixed signal extension (VHDL –AMS) and finally HDL-A. AHDL is most commonly used as a HDL language for analog circuits. SpectreHDL is a high level description language that uses functional description text files to model the behavior of the systems. Verilog-AMS is an industry standard modeling language that contains continuous an event driven simulators for analog, digital and analog/digital circuits. VHDL-AMS is good for verifying complex analog, mixed signal and RF (radio frequency) circuits. HDL-A is a proprietary HDL for mixed and analog circuits.

HDL for Printed Circuit Design: PHDL (Printed Circuit Board HDL) is generally used for modeling text based schematics for PCBs. It allows generating massive buses and re-uses device definitions easily.

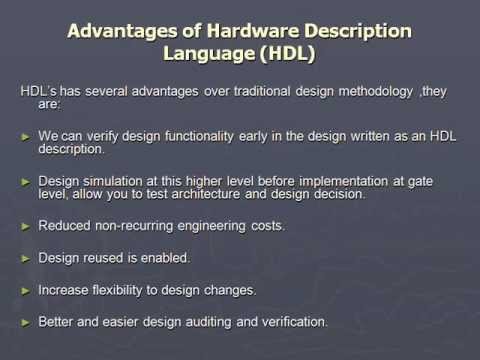

Benefits of HDL

The major benefit of the language is fast design and better verification. The Top-down design and hierarchical design method allows the design time; design cost and design errors to be reduced. Another major advantage is related to complex designs, which can be managed and verified easily. HDL provides the timing information and allows the design to be described in gate level and register transfer level. Reusability of resources is one of the other advantage.